西安人都注册了,还不快来?

您需要 登录 才可以下载或查看,没有账号?注册

×

10月11日,以“设计封装协同,共筑芯未来”为主题的第三届集成芯片和芯粒大会开幕。西安高新区企业北极雄芯携自主研发的货架芯粒解决方案精彩亮相,向近千名行业专家、企业代表展示了以HUB+X开放架构为核心的芯粒技术突破,为高端芯片降本增效、灵活适配下游需求提供了全新路径,引发产业界广泛关注。

大会上,北极雄芯重点推介了“功能解耦、灵活集成”的货架芯粒方案——通过通用型HUB Chiplet与功能型Functional Chiplet的组合,打破传统ASIC SoC大芯片研发周期长、成本高、风险大的痛点。

值得关注的是,北极雄芯还在大会上预告了全球唯一的HUB+FPGA原型验证平台,该平台集成12核ARM Cortex A72处理器、80TOPS高性能可重构协加速器及丰富外设接口,预计12月正式推出,将为客户提供从方案验证到量产落地的全流程支持。更关键的是,依托货架芯粒的复用性与模块化设计,北极雄芯可将传统芯片研发的NRE费用降至五分之一到十分之一,大幅缩短产品上市周期,降低企业创新门槛。

当前,全球集成电路产业正从“尺寸微缩”向“异构集成”战略转型,芯粒技术成为破解高端芯片发展瓶颈的关键。北极雄芯此次推出的货架芯粒方案,不仅实现了核心IP的量产级突破,更以开放架构构建起“IC设计商-IP提供商-封装企业”的协同生态——IC设计商可直接采购标准化IP裸片,灵活组合成定制化方案,无需重复投入大IP流片。

未来,北极雄芯将持续完善芯粒产品矩阵,以高性价比、高灵活性的解决方案,助力更多企业快速切入AI、汽车电子、工业控制等高端芯片领域,共筑芯粒产业新未来。

(高新融媒记者 于秋瑾 通讯员 马兰)

|

西安的雨,终于停了3869 人气#古城杂谈

西安的雨,终于停了3869 人气#古城杂谈 雁鸣湖四号湖上的西安东站高架快速路1666 人气#城市发展

雁鸣湖四号湖上的西安东站高架快速路1666 人气#城市发展 刘禹锡笔下的玄都观找见了!4884 人气#古城杂谈

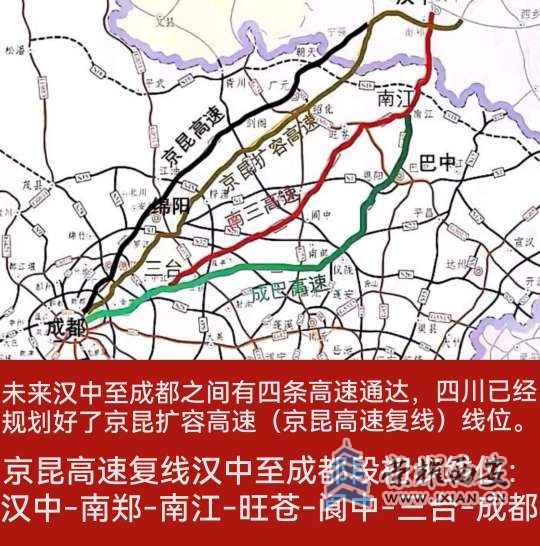

刘禹锡笔下的玄都观找见了!4884 人气#古城杂谈 京昆高速复线陕西段线路猜想6221 人气#城市发展

京昆高速复线陕西段线路猜想6221 人气#城市发展